在24 V中小功率段,市面主流方案常被“大體積+高BOM”困擾:

用PQ3230,高度>30 mm,塞不進導軌殼;

采用同步整流雖效率高,但成本立刻+3元;

變壓器參數各家保密,工程師反復試繞、燙手又燙心。

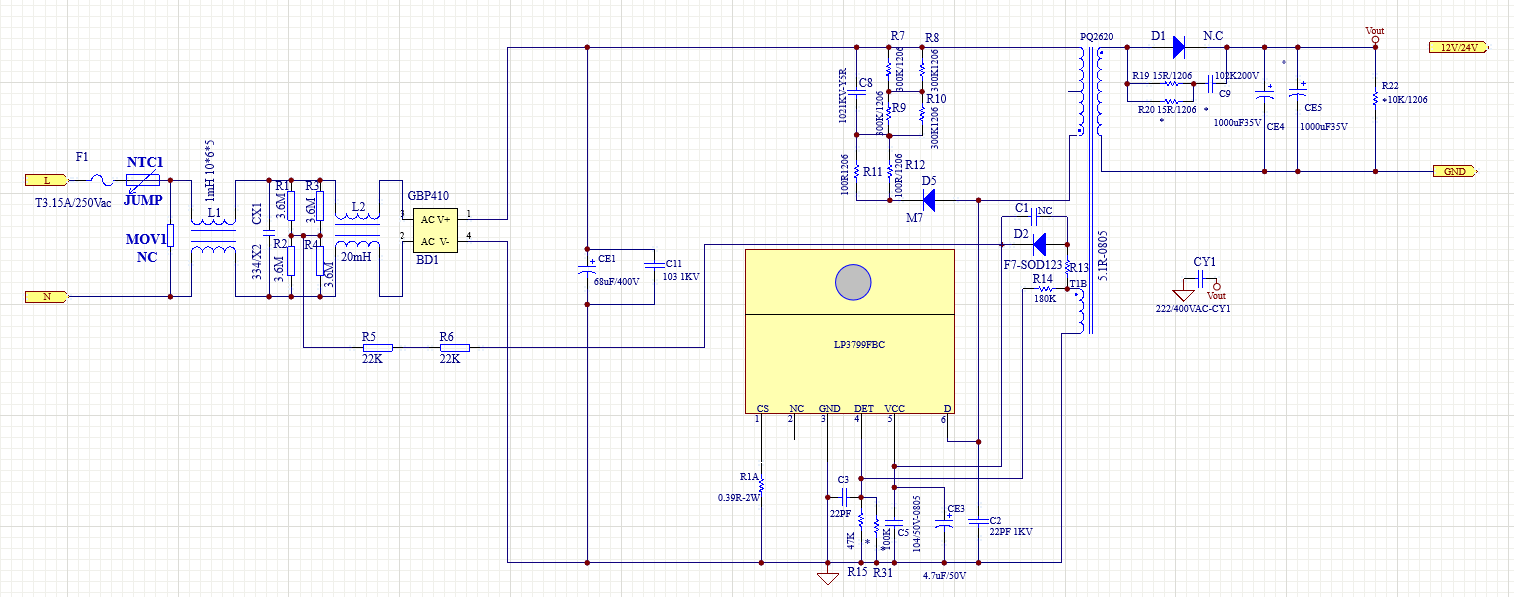

芯茂微LP3799F系列(FAC/FBC僅封裝差異,內核同源)給出了一條“PQ2620+二次側肖特基”的另類路線:

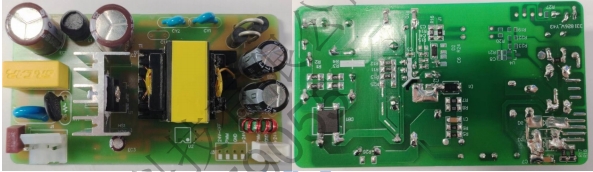

“反激、非連續、谷底導通、125 kHz”四板斧,把24 V×2.5 A=60 W功率硬生生壓進PQ2620磁芯,成品尺寸42 mm×28 mm×22 mm,自然冷卻,成本<15 RMB(不含殼)。本文把官方只給圖片的“非標原理圖+變壓器手工繞單”一次性公開,并給出可復制的PCB布局、EMI調試與安規要點,供廣大電源同行“抄作業”。

內置800 V/2 Ω超結MOS,無需外置散熱片即可60 W;

自供電專利,取消輔助繞組,變壓器腳位直接省2 Pin;

頻率折返+谷底鎖定,230 VAC滿載效率>88 %,待機<75 mW;

磁芯接地腳位可編程,EMI“熱點”自動移位,余量>6 dB;

OTP、OLP、OVP、短路自恢復全打包,過安規IEC/UL62368一步到位。

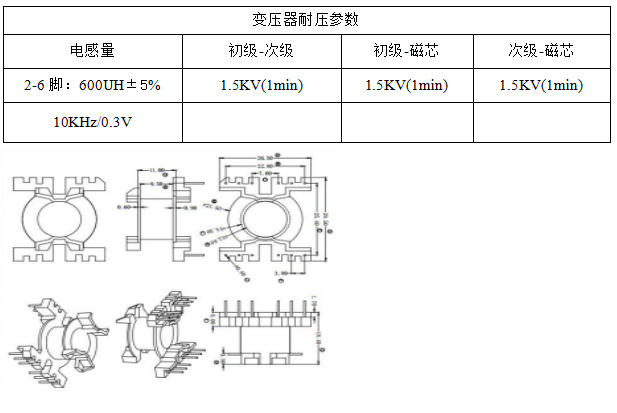

電感量LP 600 μH ±5 %,漏感<30 μH(5 %),氣隙0.15 mm(PC40材質,研磨中間柱)

1-NC,2-N1始,3-N1末/N6始,4-N2始,5-N2末/N5始/磁芯接地,6-N6末,8-N3末,12-N3始

→ 注意:5腳為“磁芯+次級公共地”,與PCB銅皮大面積相連,一舉解決EMI與ESD

N1:φ0.45 mm×1,36 T,密繞2層,2→3,3層高溫膠帶

N2:φ0.2 mm×3,7 T,密繞整層,4→5,3層膠帶

N3:φ0.65 mm三層絕緣線,10 T,密繞整層,12→8,3層膠帶(安規“雙重絕緣”)

N5:φ0.2 mm×2,12 T,5→NC,屏蔽層,單端浮空,降低共模

N6:φ0.4 mm×1,14 T,3→6,補償繞組,輔助芯片自供電(官方取消,但預留更穩)

起繞腳加鐵氟龍套管,杜絕“錫尖”刺破膠帶

每層膠帶≥3層,重疊>50 %,過1.5 kVac耐壓

繞完真空含浸,防止音頻噪聲

成品測試:1 kHz/0.3 V下LP 600 μH ±5 %,漏感<30 μH,Q>60

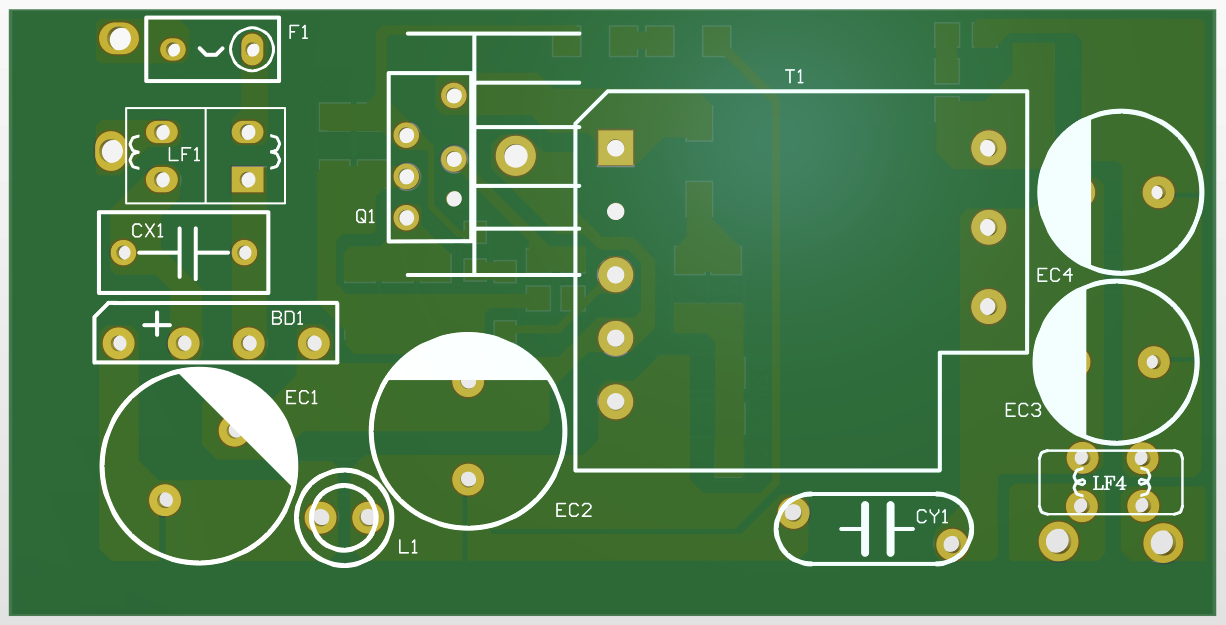

直流母線→變壓器→MOS→RCS→母線地,環路面積<1 cm2,差模輻射下降6 dB

芯片GND腳→RCS下地→EC1負→母線地,星型連接,杜絕共阻彈跳

R19/R20分壓地單獨回芯片GND腳,遠離SW節點,誤差<±1 %

肖特基陰極→CE4/5→變壓器次級地,銅皮上下夾芯,降低ESL

頂層MOS漏極銅箔>200 mm2,反面開窗打散熱過孔,60 W溫升<45 K

磁芯5腳銅皮預留RC Snubber(100 Ω/1 nF),暗室不過時直接補焊,無需割線

| 負載 | VOUT | IO | Pin | η | Vripple | 殼溫 |

|---|---|---|---|---|---|---|

| 100 % | 24.2 V | 2.50 A | 68.2 W | 88.7 % | 120 mV | 65 ℃ |

| 75 % | 24.2 V | 1.88 A | 51.6 W | 88.1 % | 100 mV | 58 ℃ |

| 50 % | 24.2 V | 1.25 A | 35.1 W | 86.3 % | 85 mV | 52 ℃ |

| 25 % | 24.2 V | 0.63 A | 18.9 W | 80.7 % | 70 mV | 45 ℃ |

| 0 % | 24.2 V | 0 A | 0.07 W | — | 40 mV | 35 ℃ |

待機功耗70 mW,滿足CoC Tier 2

傳導EMI:QP值余量>8 dB@500 kHz,無共模電感即可過Class B

浪涌:±2 kV差模/±4 kV共模,輸出無復位

短路:自恢復,打嗝模式,MOS尖峰<650 V(800 V耐壓余量23 %)

LP3799FAC/LP3799FBC 這顆“老炮兒”芯片,只要變壓器繞得溜,就能從 18W 干到 60W。本文把原理圖、PCB、變壓器繞制數據、全套實測數據全部開源,歡迎直接打樣。