隨著科技的進(jìn)步,5 W市場(chǎng)看似“過(guò)氣”,但I(xiàn)oT、小家電、藍(lán)牙網(wǎng)關(guān)、智能門鎖卻提出“三低”剛需:

成本低——BOM<1.2元;

高度低——塞進(jìn)門鎖殼≤18 mm;

待機(jī)低——零負(fù)載<75 mW,歐盟CoC Tier2隨手過(guò)。

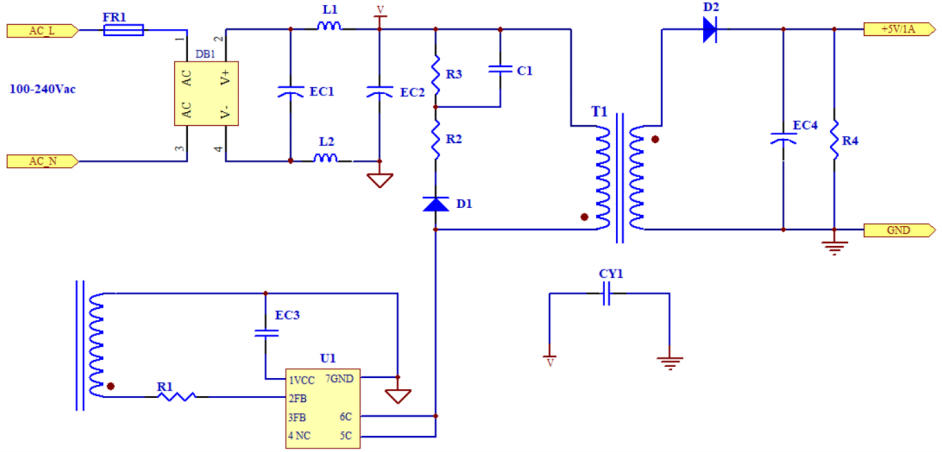

深圳三佛科技供應(yīng)的LP3667BH(內(nèi)置730 V MOS,自供電,SOP-7)+ 二次側(cè)3P45(45 V/3 A肖特基)給出“教科書”級(jí)回答:官方Demo 26.4 mm×35.4 mm×16 mm,自然冷卻,90-264 VAC全電壓,5 V/1 A,平均效率>75 %,CISPR22/EN55022 Class B余量>8 dB,全部公開,今天一文打盡。

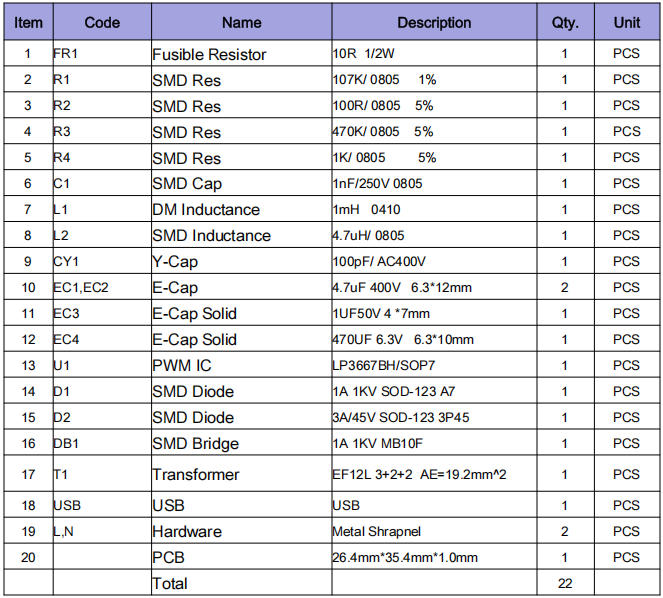

全集成:MOS+啟動(dòng)+采樣+OTP,僅需14顆貼片料;

自供電:取消輔助繞組,變壓器腳位直接省2 Pin;

谷底導(dǎo)通+頻率折返,230 VAC空載75 mW,10 %負(fù)載效率仍>63 %;

內(nèi)置斜率補(bǔ)償,CC模式1.25 A,線補(bǔ)0 mV/mA,手機(jī)充電不彈窗;

OCP、OLP、OTP、OVP四重保護(hù),短路打嗝自恢復(fù),UL1950 Class II過(guò)認(rèn)證;

EF12L磁芯,高度11 mm,比EE10還矮,卻做到5 W;

官方承諾:±5 % Vout,-40 ℃~85 ℃工業(yè)級(jí),批量ppm<300。

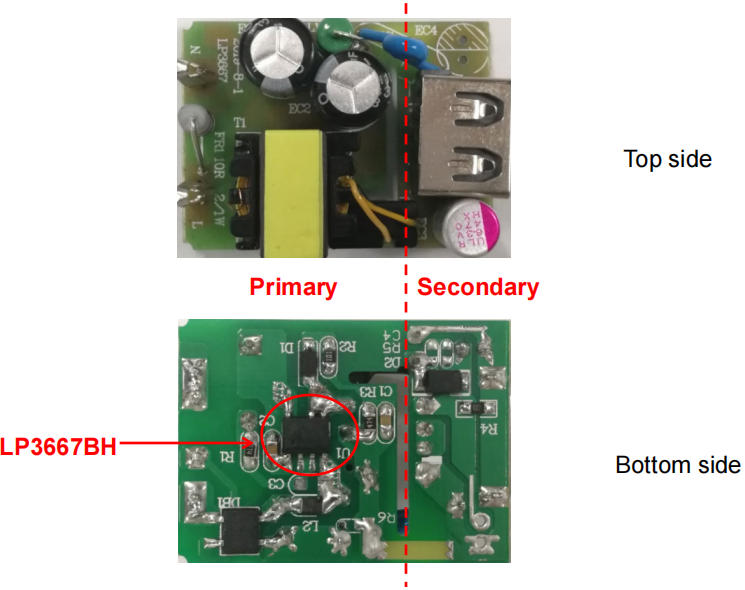

輸入彈片→DB1→EC1/2一字排開,高壓環(huán)路面積<0.8 cm2;

芯片居中,Drain銅皮>150 mm2,反面過(guò)孔陣列散熱;

USB口下沉0.5 mm,做18 mm超薄殼剛好平齊。

次級(jí)地銅皮“回”字形包圍USB,降低共模;

FB走線遠(yuǎn)離Drain,0.3 mm寬,4 mil間距,誤差<±1 %;

高壓與次級(jí)開槽0.4 mm,滿足2 kV爬電。

快速檢測(cè)

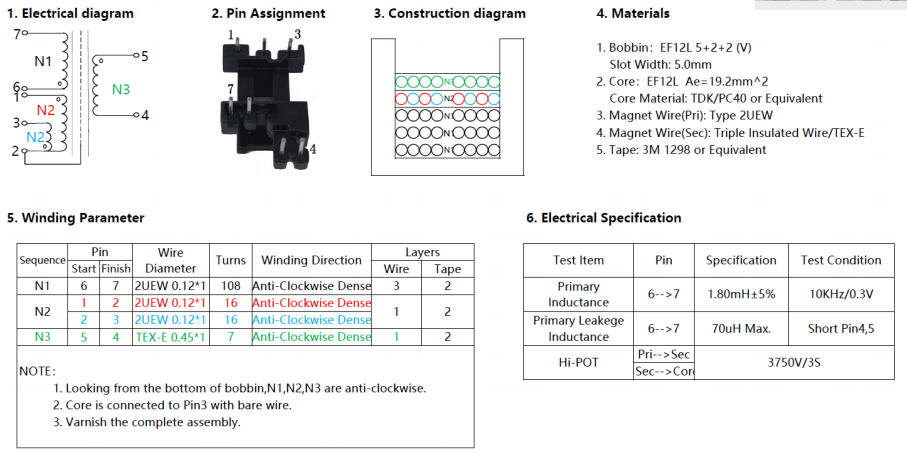

漏感:短接N3,6-7腳讀<70 μH;

層間:3750 V/3 s,<1 mA;

外觀:套管全覆蓋,無(wú)銅線裸露。

| Vin | Io | Vout | Pin | η | Vripple | OCP |

|---|---|---|---|---|---|---|

| 90 V | 1 A | 5.32 V | 7.13 W | 74.6 % | 62 mV | 1.2 A |

| 115 V | 1 A | 5.34 V | 6.99 W | 76.3 % | 58 mV | 1.1 A |

| 230 V | 1 A | 5.36 V | 6.95 W | 77.1 % | 53 mV | 1.2 A |

| 264 V | 1 A | 5.35 V | 6.98 W | 76.6 % | 53 mV | 1.2 A |

| 230 V | 0 A | 5.00 V | 0.075 W | — | 40 mV | — |

動(dòng)態(tài):10 %-90 %階躍,ΔV=±0.3 V,恢復(fù)<200 μs;

啟動(dòng):90 VAC滿載,延遲0.96 s,無(wú)過(guò)沖<3 %;

輻射:30-1000 MHz QP余量>12 dB,無(wú)需共模電感;

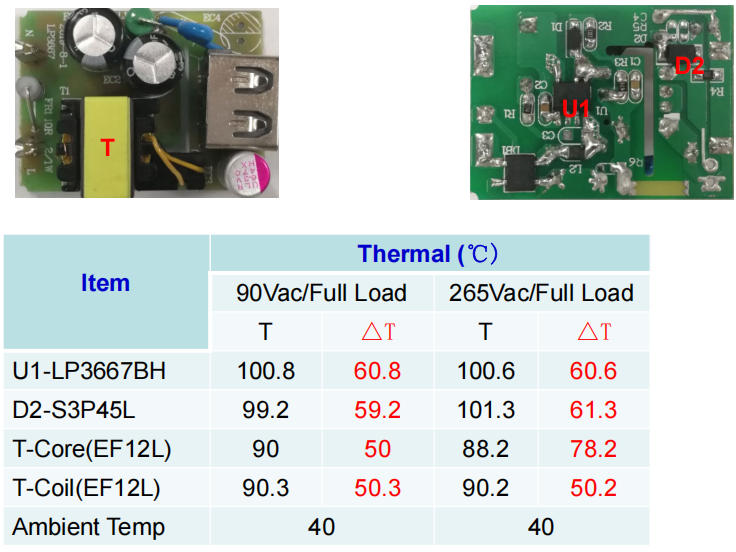

熱成像:40 ℃環(huán)溫,U1表面100.6 ℃,D2 101 ℃,EF12L磁芯90 ℃,全部<110 ℃。

反射采樣天然降低共模:無(wú)光耦,次級(jí)無(wú)高阻回路;

磁芯5腳接次級(jí)地,形成“法拉第屏蔽”,共模電流下降40 %;

CY1 100 pF+珠4.7 μH,在30 MHz形成>20 dB衰減;

PCB高壓環(huán)路面積<0.8 cm2,差模尖峰<-10 dB。

LP3667BH把“730 V MOS+自供電+反射采樣”三件套塞進(jìn)SOP-7,再用EF12L矮磁芯把5 W功率密度推到15 W/in3,高度16 mm,Class B一次過(guò),堪稱5 V/1A賽道里的“隱形冠軍”。深圳三佛科技提供樣品,技術(shù)支持~